# **Computer Architectures for Chip Surplus**

August Ning, David Wentzlaff

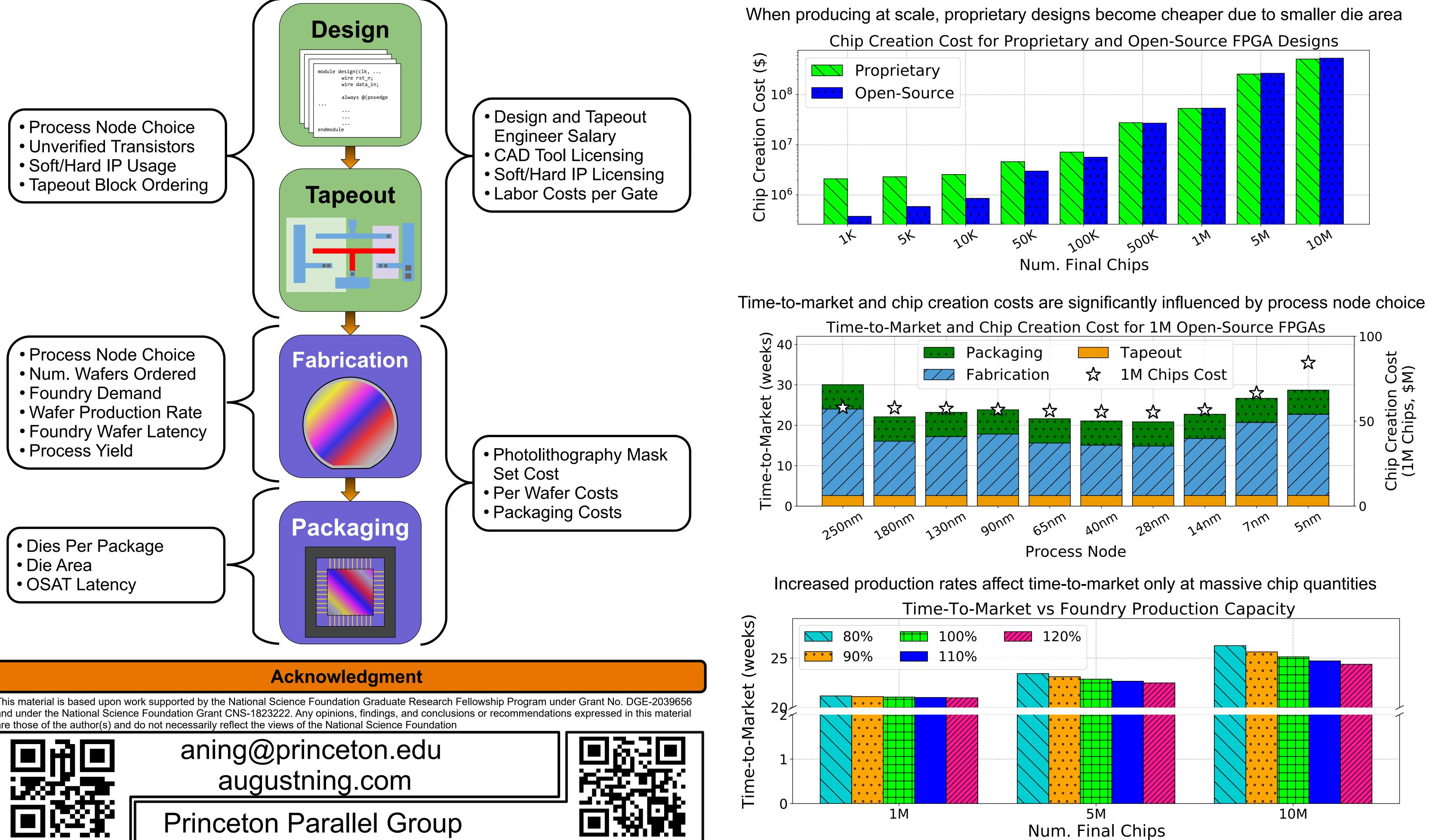

## Chip Creation is Specialized, Time Consuming, and Expensive

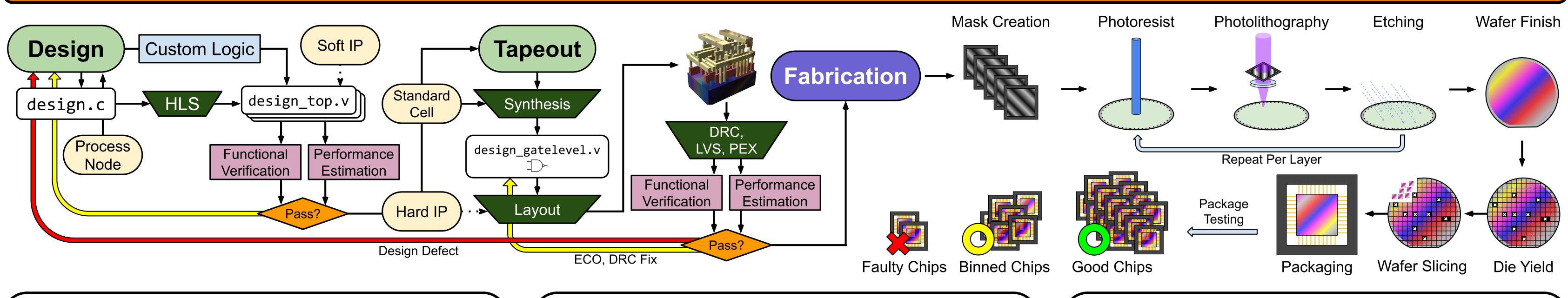

• Chip design requires expertise in chip architecture, backend tapeout flow, and verification

- Fabrication is a complex process and only few firms manufacture at the most advanced nodes

- Five semiconductor foundries control 90% of pure-play production capacity

- Chip designs take require multiple iteration to meet performance, cost, and area constraints

- Synthesis, layout, and verification take significant engineering effort and compute time

- A single wafer may take 12-20 weeks to complete fabrication and additional time to complete packaging

- Chip design CAD tools, IP, and PDKs generally require expensive licenses

- Specialization and expensive raw inputs means photolithography masks and wafer costs dominate

- Few competitors and market monopolies mean foundries have low pressure to reduce prices

### **Time-to-Market and Moonwalk Cost Modeling**

# **Evaluation**

This material is based upon work supported by the National Science Foundation Graduate Research Fellowship Program under Grant No. DGE-2039656 and under the National Science Foundation Grant CNS-1823222. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation